| クリックで拡大写真↓(協力会社と共同開発製品) |

|

|

|

・ML-IIIの本体です.

・IPMate-PCI-VX2-001をベースに

IPMate

Daughter-Cardの

IEEE1394.a GPLynx+PHY(TI社)を実装しています.

LINKチップ:TSB41LV32

PHYチップ:TSB21LV03A

・100M,200M,400Mの転送速度.

・Isochronousデータ用に128MbyteSDRAM(SODIMM)

・PCI32インタフェース(PCI64まで拡張可能)(3.3Vです.)

・PCIの代わりにExternal Connector(100pin

X 2 + 64pin X2)を利用することによりEmbedded評価にも利用可能.

・FPGAにXilinx社Virtex-II搭載.

・Daughter-Cardの差し替えで,今後,

FFM-LINK+PHYや,

IEEE1394.bにも対応予定.

・IEEE1394以外のアプリケーションにも使い回せます.

|

|

・オープンラックに実装した写真です.

・オープンラックは「玄人志向」(tm)の「ど根性試し用まな板」(tm)をベースに,使いやすいように一部加工しています.

・MotherBoardはGigaByte GA-7DPXDW-P(Athlon-XP)です.

他には,

Tyan S2518xx(Pentium-3)や,ASUS A7M266-D(Athlon-MP)でも確認しています.

|

|

・オープンラック側面からの写真です.

・左側のDaughter-CardがIEEE1394.a GPLynx+PHY-TIです.

・PHY用の電源として+12Vをパソコン本体からケーブルで取っています.

・右側のSODIMMソケットに市販の128MByteSDRAMが実装されています.

|

|

・ML-III同士を対向して試験している写真です.

・ML-IIのマッピングを極力踏襲したIO Mapped

onlyタイプと,

メモリ空間にMapしたタイプでの動作確認を行っています.

|

|

・ML-III(右側)とML-II(左側)の対向でデバッグしている写真です.

・左側のディスプレーにはML-IIのGUI画面が,

右側のディスプレーにはDOS画面が表示されています.

・DOS画面からIOやメモリ空間にアクセスしてデバッグしています.

|

|

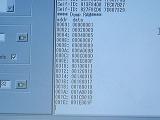

・DOS画面からCFR(Configration Register)を読みにいった画面です.

・IOアドレスc450hからCFRが始まり,

C450h(CFRの00h番地)にVersion Registerの値"7115_38A0"が,

C484h(CFRの34h番地)にBusReset Registerの値が読み出せています.

NodeNumberが3になっていることが判ります.

|

|

・ML-IIから送信したIsochronousデータが,ML-IIIのメモリダンプ画面で表示されているのがわかります.

|

|

|

・ML-IIIからML-IIへ転送したデータが表示されているのがわかります.

|

|

・参考にOpenRackの写真です.

・ハードディスクをリムーバブルにしていますので,写真のシステムではWin98SE,

Win2000, WinXP, RedhatV7上でハードデバッグが可能です.

・写真右側に積んであるのがハードディスクです.

・写真中央に挿入途中のハードディスクが見えます.

|